Технические характеристики

5576РС1У

Микросхема 5576РС1У представляет собой ПЗУ с электрическим перепрограммированием Flash-типа с последовательным интерфейсом ёмкостью 4 Мбит для конфигурирования ПЛИС.

Микросхема 5576РС1У предназначена для работы в качестве загрузочного ППЗУ с возможностью электрического программирования и стирания для конфигурирования ПЛИС серии 5576ХСхх, и ПЛИС фирмы Altera серий EPF10K50, EPF10K100, EPF10K200.

Используется для работы в радиоэлектронной аппаратуре специального назначения.

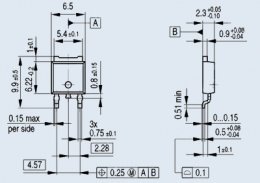

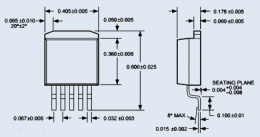

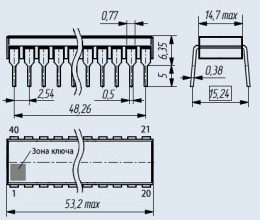

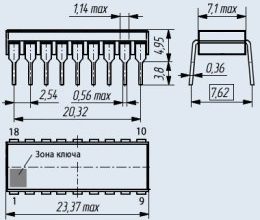

Микросхема 5576РС1У выпускается в плоском 28-выводном металлокерамическом корпусе с жёсткими выводами для монтажа на печатную плату.

Маркировка микросхемы и схема соединения электродов с выводами указывается на корпусе.

Тип корпуса: Н09.28-1В.

Категория качества «ВП».

Технические условия:

— приёмка «5» — АЕЯР.431210.710ТУ.

Основные технические и эксплуатационные характеристики микросхемы 5576РС1У:

● информационная ёмкость 4 Мбит;

● напряжение питания от 3,0 до 3,6 В;

● интерфейс JTAG IEEE Std. 1149.1;

● период следования импульсов тактовых сигналов не более 30 нс;

● период следования импульсов тактовых сигналов на входе не менее 100 нс;

● ток потребления в режиме хранения не более 1 мА;

● динамический ток потребления в режиме конфигурирования не более 50 мА;

● рабочий диапазон температур от -60 до +125 °С.

Характеристики конфигурационной схемы:

● простой в применении 4-проводной конфигурационный интерфейс ПЛИС;

● конфигурационная схема для загрузки ПЛИС 5576ХС3Т и 5576ХС4Т;

● поддержка режима конфигурирования passive serial (PS) и active serial (AS);

● низкое потребление в процессе конфигурирования и близкий к нулю ток в режиме хранения;

● толерантность выводов к напряжению +5 В;

● поддержка программного обеспечения Quartus II фирмы «Altera»;

● конфигурационное устройство включает перепрограммируемую память FLASH-типа:

— гарантированное количество циклов стирания 100.000;

— время сохранения данных 100 лет при температуре +85 °С;

— внутрисхемное программирование (ISP) через IEEE Std. 1149.1 JTAG интерфейс;

● SP схема совместима с IEEE Std. 1532.

● поддерживает программирование объектных файлов (.pof) из Quartus II посредством USB Blaster, MasterBlasterTM, ByteBlasterTM II, EthernetBlaster или ByteBlasterMVTM загрузочного кабеля;

● вывод nINIT_CONF позволяет с помощью JTAG инструкции «INIT_CONF» инициировать процесс конфигурирования ПЛИС;

● встроенный регулятор напряжения +2,5 В (до 20 мА) для питания ядра;

● встроенная схема формирования высоковольтного напряжения программирования и стирания;

● встроенная схема сброса при включении питания с изменяемым временем задержки (2 мс или 100 мс) посредством вывода PORSEL;

● возможность выбора источника конфигурационного синхросигнала:

— частота с вывода EXCLK до 33 МГц в режиме PS; — частота с внутреннего генератора 5 МГц в режиме PS;

— частота с вывода DCLK ПЛИС в режиме AS;

● технологический процесс 0.25 мкм.